Open source FPGA development on a tiny budget

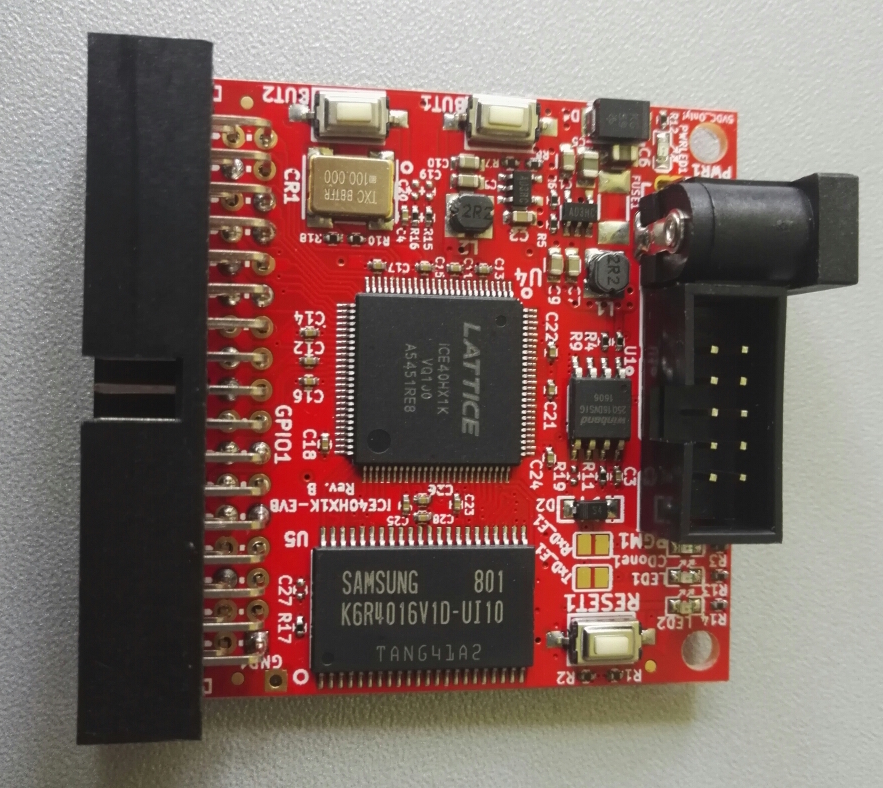

Last week, I have received the delivery of an Olimex iCE40HX1K-EVB FPGA development board. This board contains a small Lattice iCE40-series FPGA with 1280 LUTs as well as a 256k x 16 SRAM.

The exciting thing about this board (apart from its low price) is that the bitfile format of the iCE40 FPGAs has been reverse engineered, which made a complete open source toolchain possible that is able to synthesize Verilog code. The Verilog synthesis is handled by the Clifford Wolf's yosys suite, which is integrated into the IceStorm toolchain.

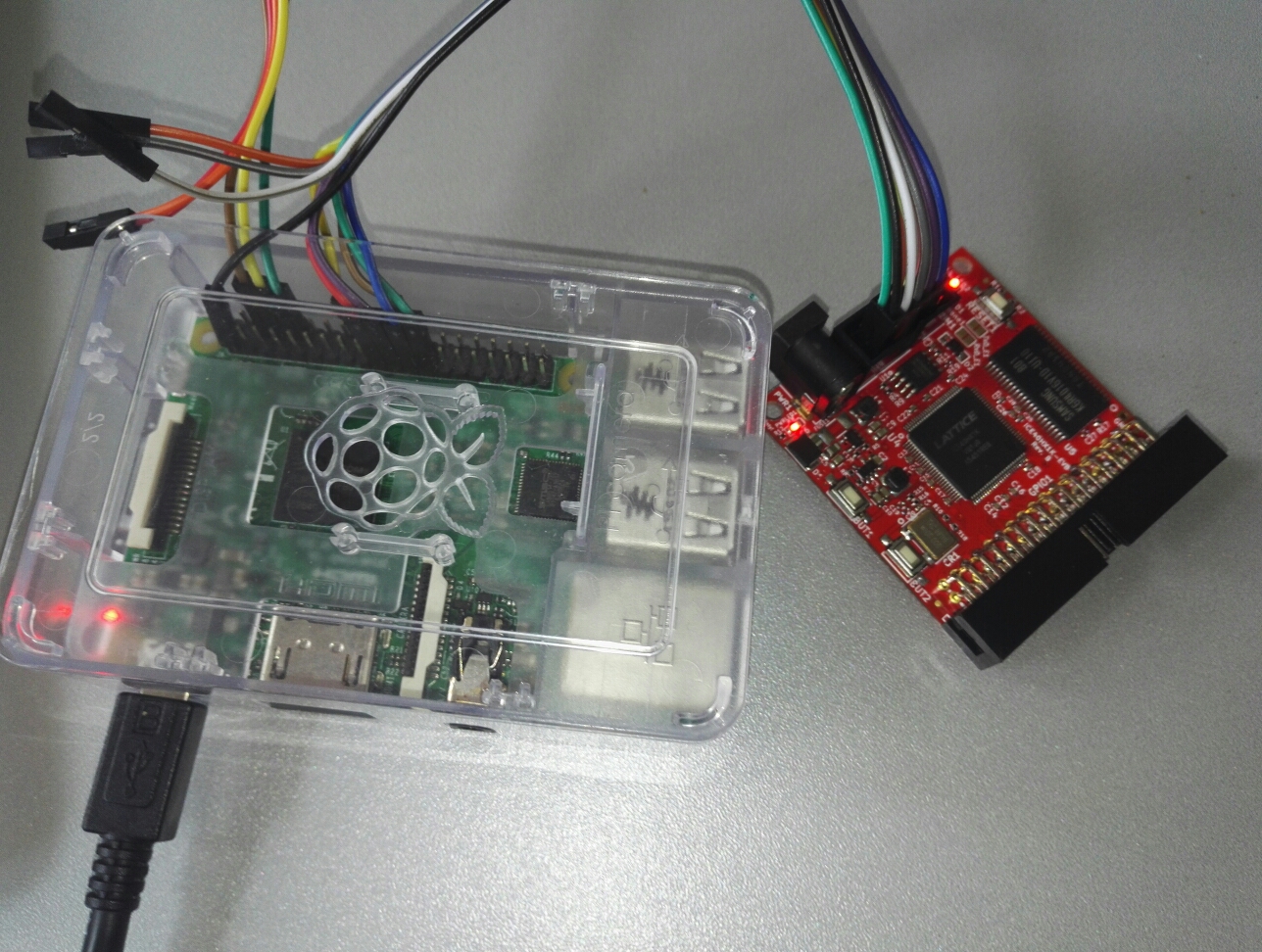

The synthesis does not need large amounts of computing power -- and since all components are open source, I was able to run all tools (including programming the FPGA via SPI) on a Raspberry Pi 3! This probably makes it one of the smallest FPGA development systems...

At the moment, the board is running some simple SRAM test code. I am trying to squeeze a tiny SoC onto the FPGA. James Bowman's J1 Forth CPU should fit, it will be interesting to see if a slightly bigger core, such as Niklaus Wirth's RISC0 core, will fit together with a few peripherals.

Tags: FPGA, Lattice, RaspberryPi, yosys, icestorm, open source