Small is beautiful!

If you got into contact with computers in the 1980s (at least in Europe), there's a good chance that you have learned to program in Pascal, one of the languages designed by Prof. Niklaus Wirth at ETH Zürich.

Even though he is retired for several years now, to this day Prof. Wirth continues to design software and even hardware systems that follow the maxime "small is beautiful" - elegant and simple systems including more recent programming languages such as Modula-2 and Oberon, the whole Oberon system environment including a simple OS and a graphical user interface, and even complete computer systems. In-house designs at ETH were the early Lilith and Ceres workstations in the 1980s; more recently, Prof. Wirth designed a small RISC system on an FPGA including all peripherals that is able to run Oberon.

You can find more information on the Oberon system including all software and Verilog source code as well as a textbook describing the complete design at Project Oberon. Reading the sources is a nice project for a rainy weekend - the whole Oberon system's source code, including the compiler and GUI, is only about 10k LoC (written in Oberon, of course). The Verilog sources including the CPU, all peripheral interfaces and the video driver, amount to less than 1000 lines - impressive!

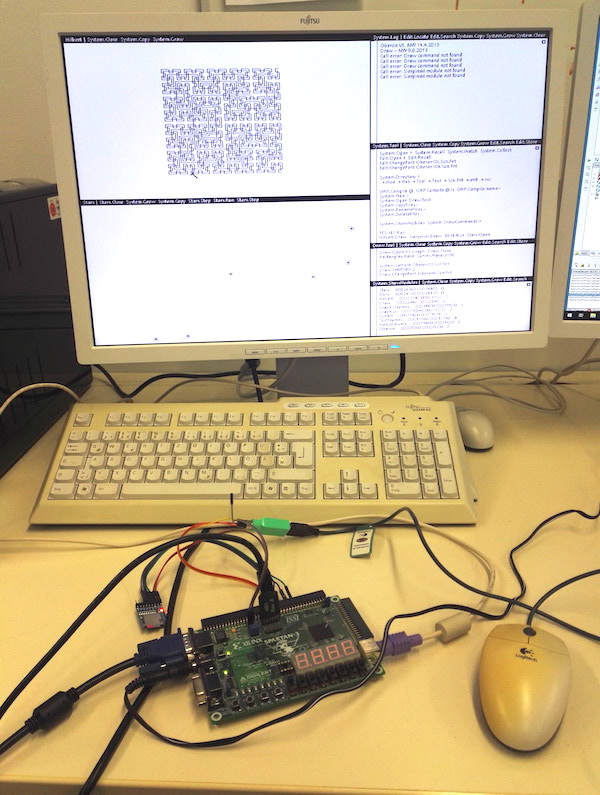

The Oberon FPGA system originally ran on a quite old FPGA board, the Xilinx Spartan 3 starter board, which features a Spartan 3S400, a tiny (by today's standards) FPGA, 1 MB of fast 32-bit SRAM, and a number of peripheral interfaces. I recently found my old Spartan 3 board and finally got the system to run.

In order to use the Oberon system, you have to connect a PS/2 keyboard and VGA monitor to the onboard ports. In addition, you need to connect an SD card (containing the Oberon file system image) and a PS/2 mouse.

For reference (you need to look it up in the ucf pinout definition file and figure out that SPI0 is the one the SD card is supposed to be connected to - SPI1 is reserved for some wireless network interface), here are the necessary connections to connector A2 on the board:

- SD MISO: A2 pin 17

- SD MOSI: A2 pin 7

- SD SCLK: A2 pin 13

- SD SSEL: A2 pin 5

- SD Vcc (3.3V): A2 pin 3

- PS/2 CLK: A2 pin 4

- PS/2 DAT: A2 pin 6

- PS/2 Vcc (5V): A2 pin 2

- GND: A2 pin 1

I have used a generic Logitech PS/2 mouse (type M-BJ69) and a Waveshare Micro-SD adapter board with a SanDisk 8 GB card.

Tags: FPGA, Oberon, Xilinx, Wirth

Open source FPGA development on a tiny budget

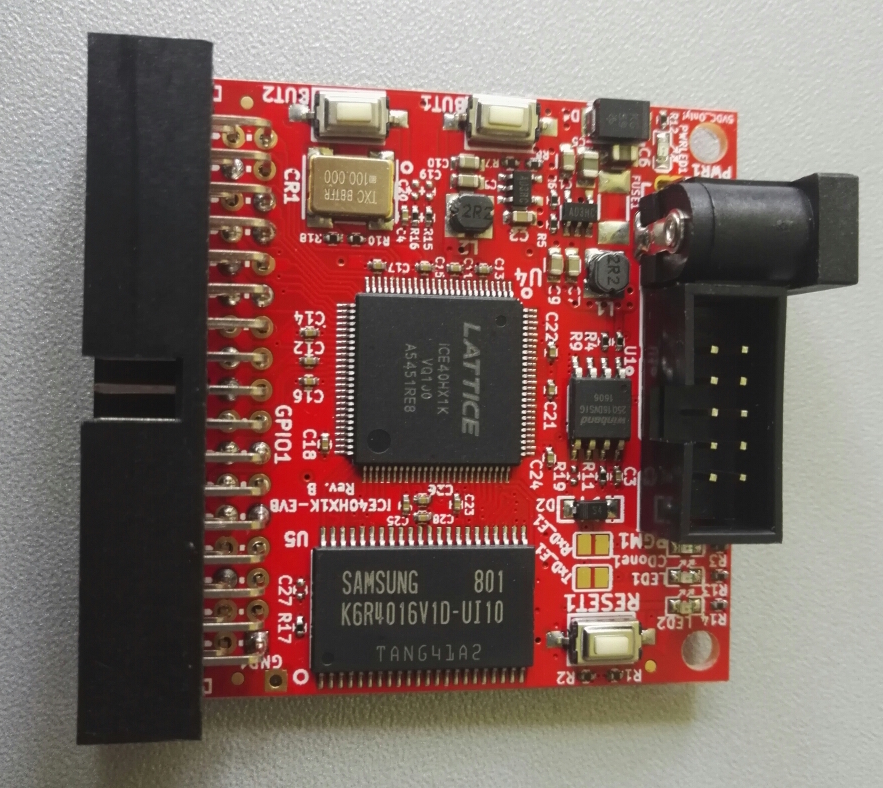

Last week, I have received the delivery of an Olimex iCE40HX1K-EVB FPGA development board. This board contains a small Lattice iCE40-series FPGA with 1280 LUTs as well as a 256k x 16 SRAM.

The exciting thing about this board (apart from its low price) is that the bitfile format of the iCE40 FPGAs has been reverse engineered, which made a complete open source toolchain possible that is able to synthesize Verilog code. The Verilog synthesis is handled by the Clifford Wolf's yosys suite, which is integrated into the IceStorm toolchain.

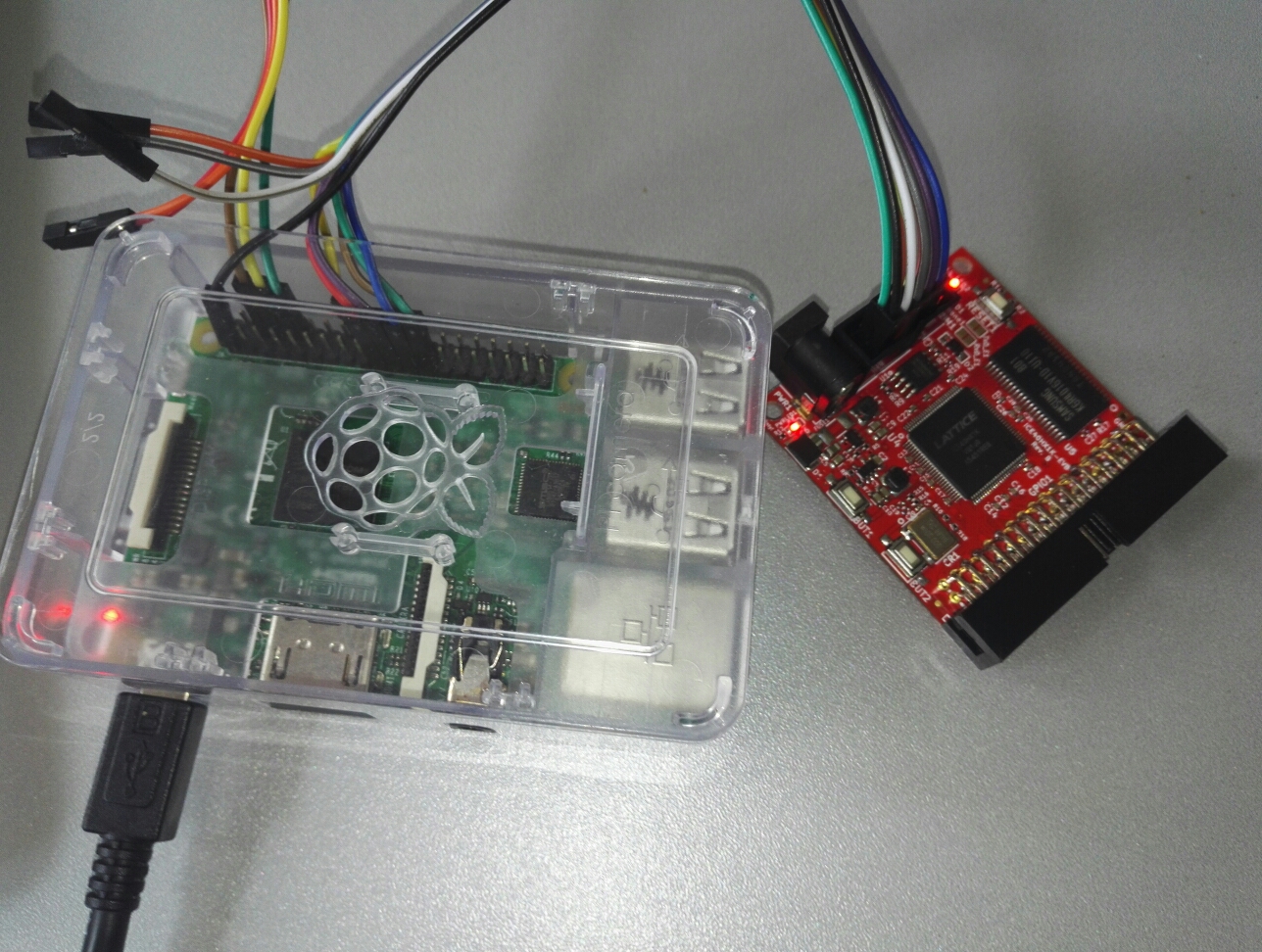

The synthesis does not need large amounts of computing power -- and since all components are open source, I was able to run all tools (including programming the FPGA via SPI) on a Raspberry Pi 3! This probably makes it one of the smallest FPGA development systems...

At the moment, the board is running some simple SRAM test code. I am trying to squeeze a tiny SoC onto the FPGA. James Bowman's J1 Forth CPU should fit, it will be interesting to see if a slightly bigger core, such as Niklaus Wirth's RISC0 core, will fit together with a few peripherals.

Tags: FPGA, Lattice, RaspberryPi, yosys, icestorm, open source